Proxy Ports vs Full Ports in SysML: Which Should You Use?

Proxy Ports vs Full Ports in SysML: Which Should You Use?

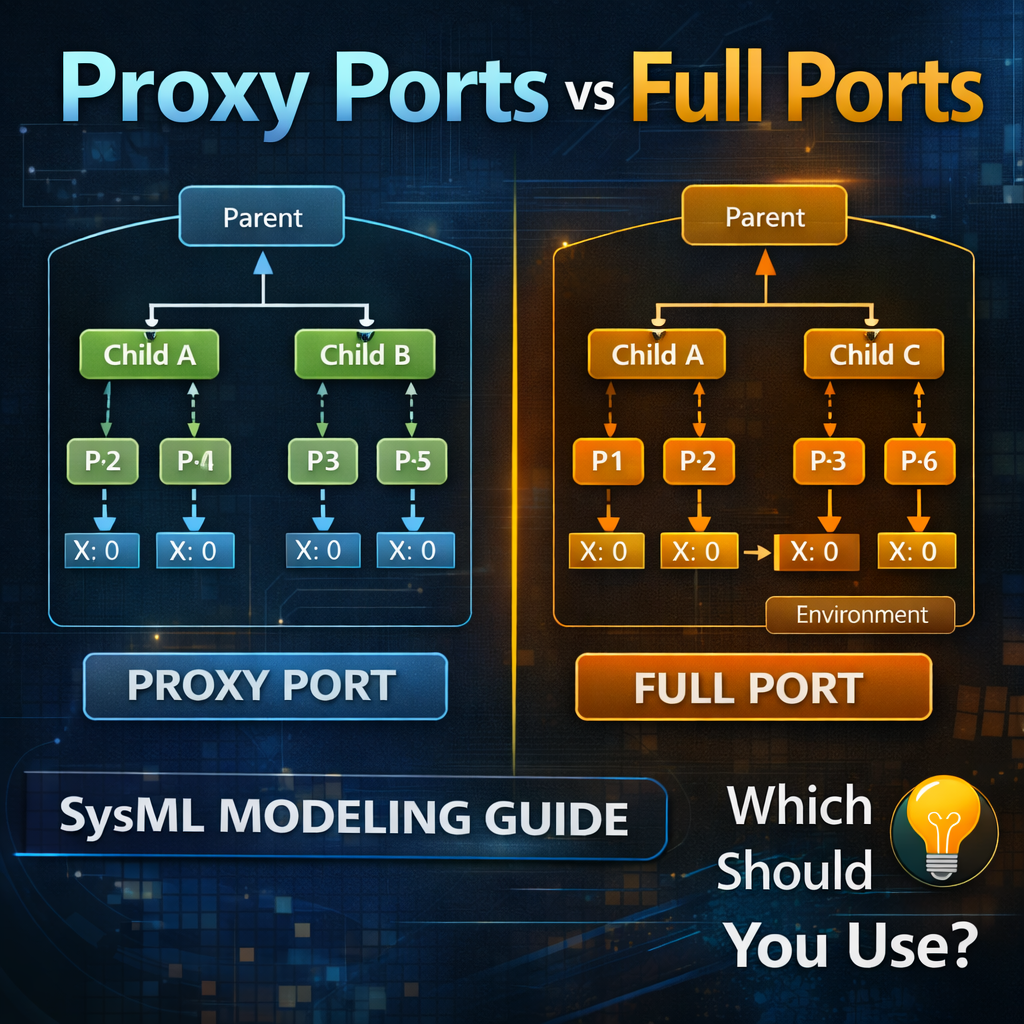

Ports are one of the most important concepts in SysML internal block diagrams (IBDs) because they define how system components communicate with each other. Two commonly used port types are proxy ports and full ports. While both enable communication between blocks, they behave very differently in simulation and system architecture modeling.

In this article, we will compare proxy ports and full ports in SysML, demonstrate how they behave in simulation, and explain why many modelers prefer proxy ports as the default modeling approach.

You can watch the full walkthrough here:

https://www.youtube.com/watch?v=sXblHYOqUFI

What Are Proxy Ports and Full Ports in SysML?

Both proxy ports and full ports are used to connect system components and allow signals, data, or events to flow between blocks.

However, they differ in how they are typed and how behavior is handled.

Full Ports

Full ports are typed by blocks. Because of this, they can execute behavior and process signals internally.

Key characteristics:

-

Typed by blocks

-

Can run behaviors

-

Often used to represent physical components

-

Can introduce additional instances during simulation

Proxy Ports

Proxy ports are typed by interface blocks. They act as a pass-through interface to the internal structure of a block.

Key characteristics:

-

Typed by interface blocks

-

No internal behavior

-

Acts as a window into the internal structure

-

Keeps architecture clean and easier to interpret

Proxy Port Example in SysML Simulation

In the first model example, the system contains several child components:

-

Child A

-

Child B

-

Child C

-

Environment

Signals are passed sequentially between the children through proxy ports.

Simulation Flow

-

Child A sends a signal to Child B

-

Child B processes the signal and forwards it

-

Child C receives the signal and increments its internal value

-

The signal continues through the model

When configured correctly using onPort parameters, the signal travels through the system exactly as intended.

The result:

-

Each component updates its internal value

-

Simulation results remain clear and traceable

-

Only one instance of each component exists

This makes debugging and system analysis straightforward.

Applying Mass Roll-Ups with Proxy Ports

After the signal behavior is validated, a mass roll-up pattern can be applied.

Using SysML roll-up patterns:

-

Each subsystem defines its mass value property

-

The parent block automatically sums the mass values

-

The total system mass is calculated during simulation

Example:

Child B Mass = 55

Environment Mass = 5

Total System Mass = 102.1

This behavior works exactly as expected when proxy ports are used.

Full Port Example in SysML

The second model replaces the proxy port on Child C with a full port.

At first glance, the diagram appears similar. However, during simulation several unexpected behaviors occur.

What Happens During Simulation?

The system accidentally creates two instances of Child C:

-

One instance associated with the full port

-

Another instance associated with the part property

Because of this duplication:

-

Signals are processed twice

-

Values appear in unexpected locations

-

Debugging becomes significantly more difficult

Even though the simulation eventually produces correct values, the internal structure becomes confusing and harder to trace.

Why Full Ports Can Be Confusing

Full ports introduce several modeling challenges:

1. Duplicate Instances

Because full ports are typed by blocks, the system may create multiple behavioral contexts, which can produce duplicated signals and behaviors.

2. Harder Simulation Debugging

Signals may appear to pass through the model correctly, but values may be stored in different internal instances, making the simulation difficult to interpret.

3. Less Clear System Architecture

Without explicit composition relationships, it becomes difficult to determine where components belong in the architecture hierarchy.

For example:

-

Is Child C part of the parent system?

-

Or part of another subsystem?

-

Or attached through the port?

This ambiguity becomes problematic in large models.

Why Many SysML Modelers Prefer Proxy Ports

Because proxy ports act as pure interfaces, they provide several architectural advantages.

Clear Architecture

Proxy ports preserve the true structural hierarchy of the system.

Easier Simulation Debugging

Signals pass through predictable paths without creating hidden component instances.

Better System Documentation

Architecture diagrams remain easy to understand for engineers reviewing the model.

Cleaner Drawings

When generating system documentation or architecture diagrams, proxy ports maintain a clear relationship between components.

Best Practice Recommendation

In most cases, proxy ports should be the default choice when designing SysML internal block diagrams.

Use proxy ports when you want:

-

Clean system architecture

-

Clear communication interfaces

-

Simpler simulation debugging

-

Consistent subsystem decomposition

Full ports can still be useful in specialized cases where port-level behavior is required, but they often introduce unnecessary complexity.

Final Thoughts

Both proxy ports and full ports are valid modeling constructs in SysML, but they serve different purposes.

Proxy ports provide:

-

cleaner architecture

-

simpler simulation behavior

-

easier traceability between components

Full ports offer additional flexibility but can introduce confusing system structures and duplicated behaviors.

For most modeling scenarios, especially when building large digital engineering models, proxy ports provide a more reliable and maintainable solution.